Aerospace Test Systems | Defense Test Systems

Custom Test Equipment for Aerospace and Defense Manufacturing

Over 300 aero-def test solutions delivered

- NI Integration Partner

You’re risk averse and your customers expect a high level of rigor because your products are mission-critical.

With over 300 aero-def test solutions delivered, our aero-def expertise is focused on test system development for mission-critical components and sub-systems.

We’ve designed and developed test systems for many types of LRUs and subcomponents used in aerospace and defense applications. For example: flight surface actuators, ECUs via emulation of connected hardware, EO/IR imaging focused on FPA/ROIC electronics, hydraulic valves, gas valves, and others that require rigorous, traceable testing.

How we can help: our capabilities & expertise

ITAR Registered

ISO 9001 certified

Manufacturing test system development

Product validation system development (including endurance/reliability/durability testers)

Real-time control

- Real-time fault monitoring

Traceable test results for compliance and data analytics

PID control loop development

Signal acquisition – e.g. pressure, vibration, load, temperature, force, distance, strain

Signal conditioning circuit board design

Communications using MIL-STD-1553, IEEE-1394b, and ARINC

Extensive automated test report generation

Test executives (see StepWise)

Want more proof points? Check out these aero-def case studies:

Manufacturing Test System – Aircraft turbine blade quality inspection

Manufacturing Test System – Aircraft turbine blade quality inspection

Improving quality by detecting blocked holes in aircraft turbine blades with an automated test system

Client – Large aerospace company

Challenge

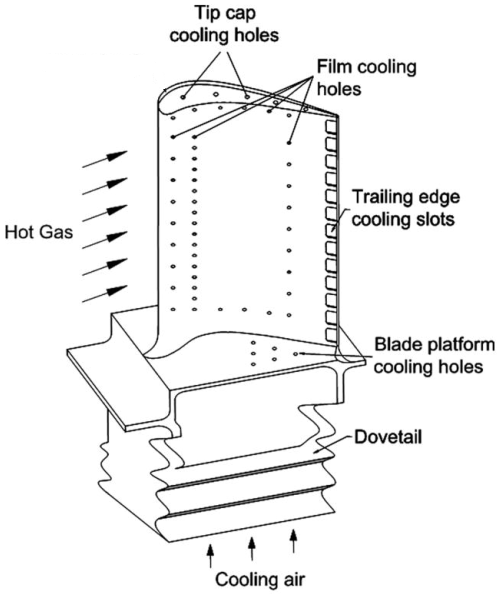

Fuel-fed aircraft turbines run extremely hot. At very high temperatures, a turbine’s blades suffer a shorter life span than if run at cooler temperatures. Consequently, turbine manufacturers put cooling holes in the blades to lower the blade temperature during operation. These holes carry cool air or gas from the blade mount along channels that eventually arrive at holes in the blade surface. This practice keeps the blade much cooler than without the flow.

Some blades have a huge number of holes. Inspecting that each hole is open and has sufficient flow is time-consuming and, if inspected by a person, prone to error due to boredom and distraction. Plus, carpal tunnel syndrome issues are present due to repetitive motions. Multiply these issues by the large number of blades in each turbine and inspection becomes a significant effort.

Our client wanted to implement an automated inspection station to increase throughput and decrease mistakes. Sending defective blades down to the subsequent manufacturing steps is pure manufacturing waste when they are rejected at some later step. Reducing operator injury was also important.

Image courtesy of CC by 4.0 https://creativecommons.org/licenses/by/4.0/ from Zhang, R.; Liu, P.; Zhang, X.; Xi, W.; Liu, J.; “Recent Developments in the Aerodynamic Heat Transfer and Cooling Technology of Gas Turbines Endwalls”. Aerospace 2023, 10, 702. https://doi.org/10.3390/aerospace10080702

Solution

Collaborating with our client, we created a manufacturing inspection system that uses an IR camera and a robot to scan different regions on the blade under inspection. The camera is placed at specific locations and at various viewing orientations to fully inspect all the holes in the blade.

A PC running a LabVIEW test application manages the entire process. Safeties and control of access to the part under inspection are included to protect personnel and product. The system uses hardware sensors and switches and some via FPGA I/O to accomplish this safety monitoring.

Benefits

- The reliability, reproducibility, and speed of the automated inspection augments the operator capabilities

- Improved part quality of parts released to downstream production steps.

- The measurements collected during inspection of each part are available for quantitative analysis of the performance of the manufacturing processes. This post-inspection information helps improve quality all around.

Working Together

This project was the culmination of over 10 years of development effort between our client and Viewpoint engineers. We started a basic R&D proof of concept system.

After some tweaks to the process and associated system redesign, we were ready to use a prototype system in a trial run situation where manufactured parts were run manually. This stage gave confidence to those in manufacturing that the system would improve part inspection while speeding up the original manual inspection process. Some changes were made at this stage to decrease costs and improve the test engineer and operator interfaces. It was then placed into the production environment.

Along this entire multi-year development path, the level of automation was increased and the system design was adjusted as we learned from each other about what worked and what didn’t. For example, early in the R&D phase, attention was paid to the analysis algorithms and data required to make those reliable and accurate. And, for the production phase, we changed hardware components to make the system less expensive and more robust while reworking the user interface to be simpler to configure and run.

Both Viewpoint and our client formed a tight team during this journey, with one constant being the Viewpoint engineers involved as the various people on the client’s side changed as this inspection system moved through departments and physical location within our client’s facilities.

System Overview

The system is composed of the following items:

- LabVIEW test application running on a PC

- Robot and motion controller

- Vision system for IR camera

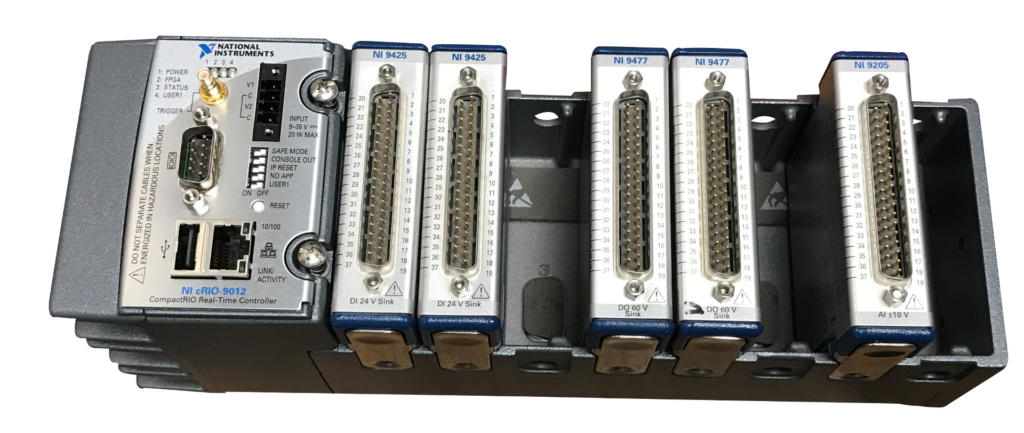

- NI Compact RIO FPGA digital I/O for controls and safeties

- NI Compact RIO analog I/O for equipment status

- Hardwired safeties and switches for operator and equipment protection

The LabVIEW application manages the entire inspection cycle:

- Assuring a part is present in the nest before starting the inspection process,

- Downloading the part-specific motion profile to the robot,

- Acquiring the images from the IR camera,

- Analyzing the images,

- Compiling the results, and

- Preparing a test report for the part.

Simultaneous with this cycle, the application checks digital and analog I/O for machine status and errors.

If a part model has not been inspected before, the LabVIEW application is used to create the motion profile for that part model.

When the test on a specific part is started, that motion profile is downloaded to the motion controller based on the part type as selected in the application.

After testing a part, the operator is presented with the test results where the option to accept, retest, or reject is offered. The operator is integral to this automated test. In any case, the test data is archived.

When the test is completed, the operator unloads the part for final disposition and loads the next part to inspect.

The LabVIEW application also has a diagnostic mode and configuration editor which is used by the operator or manufacturing engineer to evaluate and tune the inspection process.

The robot movement is managed by a motion controller based on the motion profile created via the LabVIEW application. The PC-based image acquisition is done when the motion controller alerts the LabVIEW application that the part is oriented and positioned within the field of view of the camera. Images are acquired for each of the positions defined in the motion profile.

Safety for both the operator and the part is handled in two ways. First, the Compact RIO FPGA checks system status via digital and analog inputs. Second, hardwired safety sensors and switches assure that the operator is out of the way when the robot starts moving and that the part is in the nest ready for inspection. An example of these “hard” sensors is a light curtain which will cause the system to stop if the curtain is affected during a test.

| SOFTWARE FUNCTIONS |

|---|

| NI FPGA for control and safeties |

| PC LabVIEW test application |

| System configuration |

| Data management |

| Safeties and machine status |

| HARDWARE USED |

|---|

| Articulated robot |

| Vision camera |

| FPGA digital I/O |

| FPGA analog I/O |

| Hardwired safety circuit for personnel and product protection |

| Touchscreen monitor |

Automated production test of EO/IR imaging subsystem

Automated production test of EO/IR imaging subsystem

Assessing quality of mission-critical electronics for imaging

Increased throughput by automated signal skew adjustment and pixel verification

Client – Worldwide supplier of products for aerospace and defense

Challenge

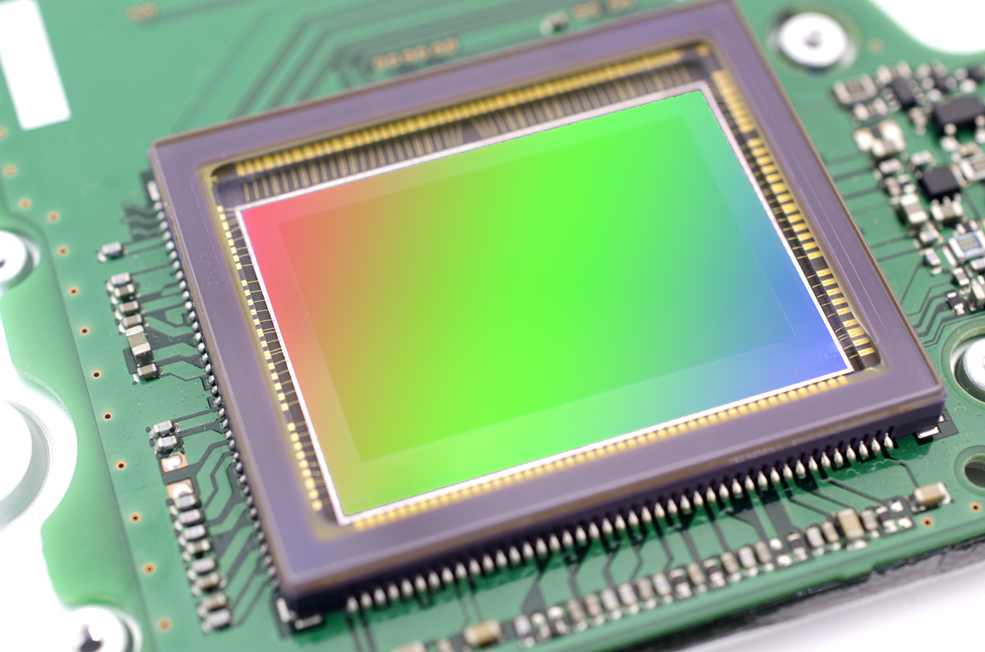

Our client wanted a test system that would significantly increase production rates for a very specialized focal plane array (FPA) and associated readout integrated circuit (ROIC) electronics.

In broad strokes, the system needed to support the following:

- Increase production test throughput as much as reasonably possible within budget and schedule constraints.

- Provide some low-code or no-code way to create new test protocols.

- Protect the DUT using hardware and software interlocks.

- Verify the correctness of test image(s) and all its pixels.

Solution

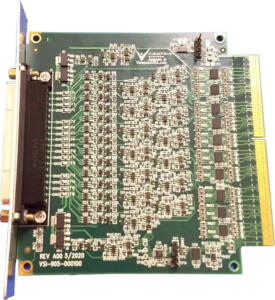

The FPA and ROIC testing for this client used many of the same techniques we have implemented for FPA/ROIC testers at some of our other clients. Thus, the solution was built around our AEDIS platform and some custom connectivity hardware which paired the DUT to the AEDIS hardware.

Specifically, the test needed to:

- Send digital signals from the AEDIS hardware to initiate and coordinate the test steps.

- De-skew bitstreams from the DUT.

- Organize and rearrange the bitstreams into image pixels.

- Provide custom “personality” modules to connect the DUT and AEDIS hardware.

- Protect the DUT from connection and power faults.

Benefits

All the bulleted items above are common requests from our clients and are supplied with the AEDIS platform or easily accommodated by design of the platform. Consequently, AEDIS often meets 80% or even 90% of typical client needs.

Thus, the client was able to cost-justify an AEDIS-based solution for two main reasons:

- overall system costs for an AEDIS-based solution were significantly less than a completely custom system and

- the increased production rates provided plenty of schedule buyback.

Furthermore, the script-based, low-code capabilities offered by AEDIS enabled:

- Support of different test images.

- Control of image transfer initiation, handling responses from the DUT, and flow.

- Version control (by the client) of script-based test configurations.

- Defined parsing of bitstreams to create the image pixels to simplify downstream image collection.

System Overview

The test system was built around AEDIS, which is a combination of five major components:

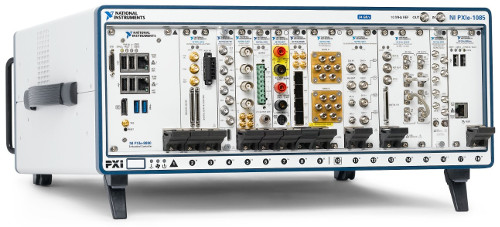

- NI FlexRIO PXI modules and chassis.

- Signal conditioning hardware.

- A REST API interface for the client’s test sequencer and LabVIEW FPGA for the hardware interfacing.

- An out-of-the-box browser-based app to interact with the AEDIS system.

- A source measure unit to supply and test the DUT’s power needs.

With this design, AEDIS acts as an instrument to incorporate into the client’s overall test system.

The NI FlexRIO modules use Xilinx FPGAs for digital I/O at the rates and channel counts required to fully test the FPA on the DUT. Some digital lines were used for commands to the FPA while most were used to receive output from the FPA.

The AEDIS interfacing hardware acts as an ITA while converting the FPA/ROIC signals to types expected by the FlexRIO. A custom “personality” module provides the physical connectivity from the client’s hardware cabling to the ITA. The AEDIS software handles the test configuration setup, data acquisition, and data storage via high-speed RAID drives.

During development of the test system, AEDIS hardware and software were also used to emulate the actual FPA and electronics to verify, before deployment, that the test system was working as required. This same setup can also be used for periodic verification as might be needed for an annual equipment performance audit.

Finally, configuration files were built from user-created scripts to give the client flexibility for adding new test capabilities for the DUT.

Some of the significant hardware and software challenges mitigated by this combination of PXI FlexRIO and AEDIS are:

- Interface to tester: The AEDIS system is treated as an instrument managed by an overall test system. The client developed some custom C# code to interface to the AEDIS REST API interface to automate their test procedures.

- DUT interfacing: Standard (keyed) cabling ran between the DUT and the custom AEDIS “personality” card to match cabling to the DUT. The output of this personality module went to the AEDIS LVDS modules.

- Channel skew: The high-frequency digital LVDS signals from the DUT can develop noticeable timing skews between channels upon arrival at the FlexRIO inputs due to signal path length differences. The test system had to detect and accommodate for these skews before combining the bits streams into bytes, then pixels, then an image.

- High data rates: Not only were the digital data output at high frequency but many channels were needed to accommodate the full frame rate of the DUT. The FPGA and the PXI backplane needed enough processing and transport bandwidth to accommodate the throughput.

- Interlocks: Keyed cabling and “signal present” software checks assured proper connections between the DUT and the AEDIS hardware before testing would begin. These safety checks were justified due to the high cost of each DUT.

- User-defined scripts: Scripts created and edited by the user provided flexibility to address future test types and system obsolescence. For example, the scripts defined details such as a) the DUT-specific commands (some of which could not be shared with us for secrecy reasons), b) when the image is being captured (or ignored), and c) if the image is stored to disk or RAM.

| SOFTWARE FUNCTIONS |

|---|

| Browser-based app for manual operation and recipe creation and editing |

| REST API interface for support of automated operation |

| Configuration of the test via scripts |

| Pre-test interlock checks |

| Data collection, bit stream processing, and mapping digital bitstream to pixels |

| HARDWARE USED |

|---|

| Standard AEDIS components for signal buffering, conditioning, and signal acquisition |

| Custom personality hardware for connectivity and physical connection interlocks |

| Signal test points in AEDIS breakout ITA modules enabled use of a logic analyzer for troubleshooting and further verification |

Replacing Wire-wrap Boards with Software, FPGAs, and Custom Signal Conditioning

Replacing Wire-wrap Boards with Software, FPGAs, and Custom Signal Conditioning

Electronic components of fielded systems were aging out

Reverse engineering effort converted wire wrap boards to FPGA-based I/O

Client – Amentum – A supplier for Military Range System Support

Challenge

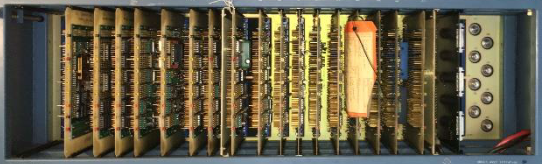

Amentum (www.amentum.com) supports a decades-old system deployed in the early 1980s. While the mechanical subsystems were still functioning, the wire-wrapped discrete logic and analog circuitry was having intermittent problems.

Systems designed and built decades ago can sometimes have wonderful documentation packets. Nevertheless, we’ve been burned too often when the docs don’t incorporate the latest redlines, last-minute changes, or other updates.

The replacement system needed to be a form-fit-function replacement to land in the same mounting locations as the original equipment with the same behavior and connections. Below is an image of the existing wire-wrap boards and their enclosure. We had to fit the new equipment in this same spot.

Figure 1 – Original wire-wrap boards

Finally, Amentum wanted to work with Viewpoint in a joint development approach. While our joint capabilities looked complementary, we didn’t know at the start how well we would mesh with our technical expertise and work culture – it turns out we worked extremely well together as a team and neither one alone could have easily delivered the solution.

Solution

Since the team treated the existing documentation package with suspicion, we adopted a “trust but verify” approach. We would use the documents to give overall direction, but we would need details from the signals to verify operation.

Leveraging Amentum’s experience with the fielded systems, the team decided early on to record actual signals to understand the real I/O behavior. We used the system’s “test verification” unit to run the system through some check out procedures normally run prior to system usage. This verification unit enabled us to use a logic analyzer for the I/O to and from the discrete logic digital signals and an oscilloscope and DMM for the analog signals. The available schematics were reviewed to assure that the signals made sense.

With a trustable understanding of system operation, Amentum created a requirements document. We jointly worked on the design of the new system. There were both an “inside” system (in a control shelter) and an “outside” system (in the unit’s pedestal).

Some overall tasks were:

- Viewpoint recommended an architecture for the inside application running on PXIe LabVIEW RT and FPGA layers.

- Amentum created the system control software on a Linux PC.

- Viewpoint developed the more intricate parts of the inside application and mentored Amentum on other parts they developed. This work recreated the existing discrete logic and analog I/O using PXIe NI FPGA boards.

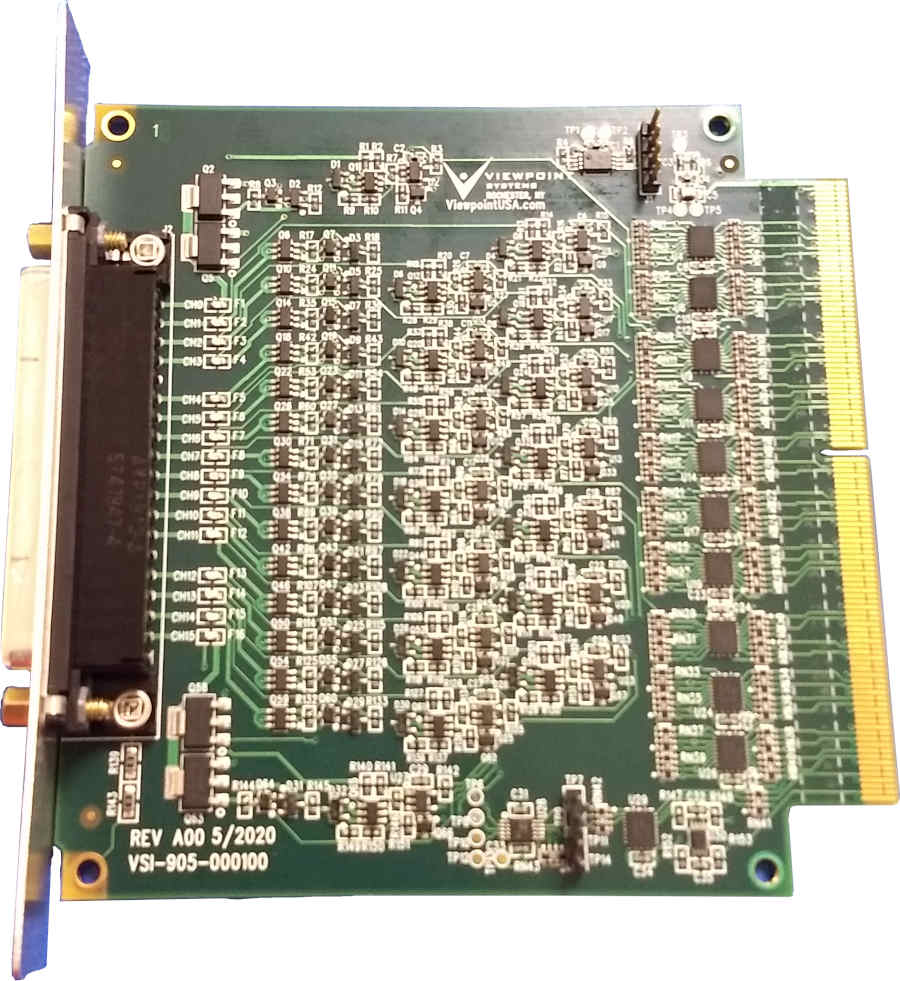

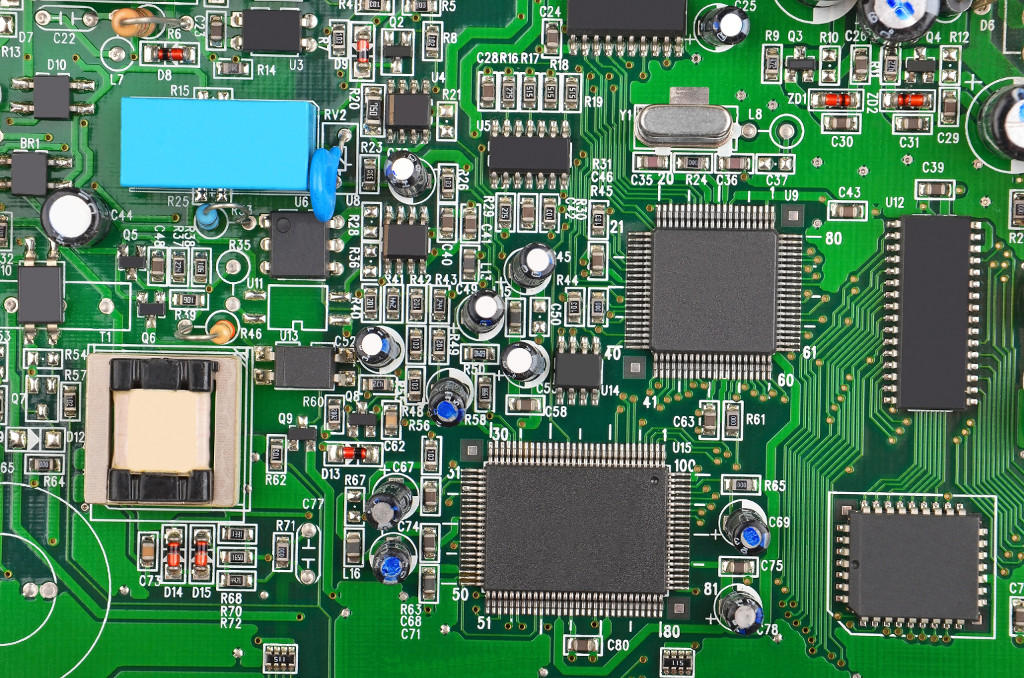

- Viewpoint designed custom interposer boards to connect harnesses to the NI PXIe equipment, including a test point and backplane boards.

- Amentum designed and developed the cRIO-based outside system application and Viewpoint created a set of custom interposer boards to connect harnesses to the cSeries modules.

The PXIe FPGA boards handled the required 60 MHz clock-derived signals with correct phases, polarity, and so on. Furthermore, the wire-wrap boards were register-based so the PXIe had to decode “bus signals” sent over a Thunderbolt bus to emulate the programming and readouts from the various wire-wrap boards.

Figure 2 – PXIe replacement to wire-wrap boards

Amentum wanted to be able to support the LabVIEW FPGA VIs used to replace the functionality of the discrete logic. So, Viewpoint acted as mentor and code reviewer with Amentum to ramp them up on using LabVIEW FPGA effectively. Neither one of us alone would have been successful coding the applications in the allotted time. Joint knowledge and experience from both Viewpoint and Amentum were required.

Signal conditioning and harnesses needed to be reworked or replaced as well, of course, since the landing points for the wires were different in the new system. Viewpoint suggested a technique, which we’ve used frequently in past obsolescence upgrade projects, to create PCB boards that accepted existing connectors.

For the cRIO, these interposer “connection” PCBs plugged directly into the cRIO cSeries module. For the PXIe, these interposer PCBs accepted the field wiring connectors and converted them to COTS cables that connected to the PXIe modules. These interposer PCBs could have signal conditioning incorporated as needed. This approach significantly reduced the need for custom harnesses. All told, about 200 signals were passed between the PXIe and various other subsystems, and about 100 for the cRIO. This approach saved significant wiring labor and cost.

Figure 3 – cRIO with interposer boards between cSeries and field harnesses

The work to design and build the signal conditioning custom electronics was split between Viewpoint and Amentum. Viewpoint did more design than build and handed over the schematics and Gerber files to Amentum so they could manage the builds while also being able to make modifications to the boards as needed.

Benefits

Amentum wanted an engineering firm that was willing to work along side them as a partner. Joint discussions about architecture and design led to a collaborative development effort where Amentum benefited from Viewpoint’s extensive expertise and guidance on LabVIEW architectural implementation and FPGA coding style.

The main outcomes were:

- As a partner of the team, Viewpoint acted as staff augmentation by providing experienced engineers with technical capabilities that Amentum initially lacked.

- This team approach delivered a stronger product to the end-customer more quickly than either of us could do alone.

- The combination of Viewpoint’s and Amentum’s experience reduced the amount of reverse engineering needed due to the lack of firm requirements.

- Reduction of electronics obsolescence by using software-centric FPGA-based functionality. Recompiled LabVIEW FPGA could target future boards models.

- Increased software-based functionality simplifies future updates and modifications.

- Decrease in number of parts leading to simpler maintenance.

- Lower wattage consumed eliminated need for an anticipated HVAC upgrade.

- Cybersecurity concerns were reduced by using Linux-based systems and FPGA coding.

System Overview

Using software to emulate the old hardware was a critical success factor. Since the requirements were not 100% solid at the start of the project, some field-testing was required for final verification and validation. The flexibility of the software approach eased modifications and tweaks as development progressed. A hardware-only solution would have necessitated difficult and costly changes. For example, some of the changes occurred very near the final deployment after the system was finally connected to an actual unit in the field.

| SOFTWARE FUNCTIONS |

|---|

| Emulate original discrete logic functions via FPGAs |

| Emulate original analog signal I/O |

| Overall system control via Linux PC |

| Maintain the same user experience as existed before |

| Modern application architecture for simpler maintenance |

| HARDWARE USED |

|---|

| NI cRIO chassis with various cSeries modules |

| NI PXIe chassis with FPGA modules to handle all the analog and digital I/O via a combination of multifunction and digital-only cards |

| Custom PCBs for signal conditioning and connectivity |

Custom FlexRIO Adaptor Module supports HIL Test Upgrade

Custom FlexRIO Adaptor Module supports HIL Test Upgrade

A custom-COTS approach reduces cost and delivery time.

Client – Major National Research Lab

Challenge

Our client has a client (the end-user) for which they developed an HIL test system several years prior. Parts were obsolete and the system needed an upgrade. The prior system had many custom-designed electronic components which could not be replaced without a complete redesign.

Consequently, our client wanted to use COTS. However, one device needed 28 VDC digital I/O, a couple of lines which carried significant current (amp, not milliamp, levels) and at switching rates much higher than a COTS solid state relay could provide.

Solution

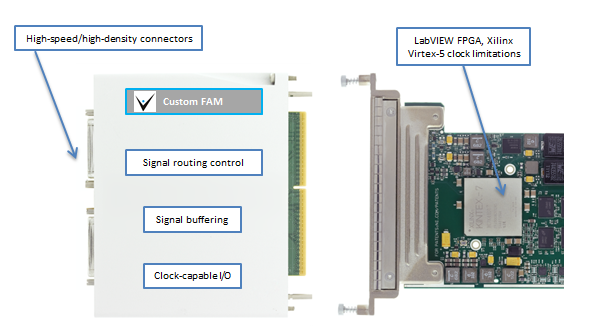

Viewpoint reviewed the requirements and created a hybrid COTS-custom solution. We combined an NI FlexRIO module with a custom FlexRIO Adapter Module (FAM) for the front end to satisfy the 28 VDC signals levels and required current drive.

Benefits

- COTS FlexRIO integrates into the remainder of our client’s PXI-based test system.

- The Custom I/O was designed for flexibility. Our client can use this FAM for both their initial end-user and other programs / clients too.

- Reduced cost relative to a completely custom solution.

- Delivery time reduced by months relative to a custom solution

FAM Overview

The custom FAM interfaced with the NI FlexRIO module, which offered low-level digital I/O (3.3 V logic), to digital signal conditioning hardware that provided the 28 VDC signal levels and required current drive.

Each I/O pin was configurable as input or output (source or sink). Each bank of 4 channels had an adjustable threshold level set via an adjustable DAC output. Some of the channels are designed for amp-level current drive, while the remainder were 250 mA. All I/O was fused appropriately.

Viewpoint also developed LabVIEW FPGA and VHDL to enable our client and the end-user to:

- Configure the I/O as in or out.

- Communicate to the DAC to allow custom input threshold trigger levels.

- Read and write the digital data.

| SOFTWARE FUNCTIONS |

|---|

| Set the direction of each of the DIO channels |

| Set the threshold level on the input channels |

| Read / Write DIO Data |

| End User Application |

| HARDWARE UTILIZED |

|---|

| COTS NI FlexRIO |

| Custom FlexRIO Adaptor Module(FAM) |

| INTERFACES / PROTOCOLS |

|---|

| Customized VHDL Component Level Intellectual Property (CLIP) integrated with LabVIEW FPGA |

| LabVIEW FPGA as required along with LabVIEW and TestStand |

High-Speed Digital Subsystem Emulator

High-Speed Digital Subsystem Emulator

Client: A large company involved in C4ISR

At maximum throughput, the AEDIS systems needed to consume and produce more than about 800 MB/s/slot.

Background

A large company involved in C4ISR was developing a system for a new high-speed digital sensor device. Viewpoint was contracted to build a test system used in design validation and ultimately endurance testing of the sensor. Since the sensor was a component of a larger system which was being developed at the same time, another test system was created to simulate the sensor by feeding signals into the system. This ability to use HIL testing for both the sensor and the downstream sensor electronics enabled parallel development, thus saving time and reducing schedule.

Challenge

Both the amount of data and the frequencies of the various digital signals were nearly at the limit of hardware capabilities. At maximum throughput, the systems needed to consume during record and produce during playback about 800 MB/s/slot. The FPGA clock on the FlexRIO had to run up to 300 MHz. The skew between triggers for data transmission needed to be less than 5 ns even between multiple FlexRIO cards even when the parallel data paths have inherent skews associated with the sensor. Finally, the systems needed to handle clocks that might be out-of-phase.

Achieving these requirements required significant engineering design in the face of multiple possible roadblocks, any one of which could have eliminated a successful outcome.

Furthermore, as usual, the development timeline was tight. In this case, it was a very tight 3 months. Basing the solution on our AEDIS platform was critical to meeting this challenge.

Viewpoint’s Solution

To meet the timeline, we had to work in parallel across several fronts:

- LabVIEW-based application development for both record and playback

- LabVIEW FPGA development for marshalling data between the controller and DRAM

- Custom FAM circuit board design and build

- FlexRIO FPGA CLIP nodes and code for low-level data handling

Technical Highlights

This sensor had several parallel data paths of clock and data lines with clock speeds up to 300 MHz on each path requiring exacting design and build of a custom FlexRIO Adapter Module (FAM) and unique custom CLIP nodes for extending the FlexRIO FPGA capabilities. The FAM also had a special connector for interfacing to the customer’s hardware.

Additional NI hardware and software completed the system components.

Results

The choice to base the AEDIS emulators on NI hardware and software was critical to completing this project. The open architecture in both hardware (custom FAM) and software (CLIP Nodes) enabled us to include some very creative extensions to the base toolset without which the project would not have succeeded in the allotted pressured schedule and on a predetermined budget. We were able to stretch the capabilities of the hardware and software very close to their maximum specifications by combining COTS and custom much more cost effectively than a purely custom design. Further, with HIL tests, both the sensor and the sensor electronics could be developed in parallel, leading to a significant schedule buyback for our client.

LabVIEW Layers

The host application, written in LabVIEW, managed the configuration of the data acquisition and the control of the LabVIEW RT-based FlexRIO systems. The configuration primarily dealt with the number of sensor channels in use, skew settings between digital lines, and other parameters that dealt with the organization of the data passed between the sensor and the FlexRIO.

Two FlexRIO applications were written, one for record and one for playback. Each FlexRIO application was written in LabVIEW, and managed the configuration of the FlexRIO cards and the movement of data between the FlexRIO cards and the RAID drives. Note that Windows supported for the RAID driver. Between 10 and 32 DMA channels were used for streaming, depending on the number of sensor channels being used.

And, each FlexRIO application had an FPGA layer, written in LabVIEW FPGA enhanced with custom CLIP nodes. For the record application, we developed a custom DRAM FIFO on the FPGA to assist with the latencies on the PXIe bus. For the playback application, we were able to stream directly from DRAM.

FlexRIO Considerations

The FlexRIO and stock FAMs from NI were initially considered as candidates for this project. Clearly, working with commercial-off-the-shelf (COTS) components would be most effective. Three options were available at the project start which could accommodate the required clock frequencies, but none offered both the required channel counts and skew/routing limitations. Hence, we had to design a custom FAM. This decision, made before the start of the project, turned out to be wise in hindsight because the parallel development path resulted in some shifts of sensor requirements which could be accommodated with the custom FAM but might have led to a dead-end with a COTS FAM.

FlexRIO CLIP

In LabVIEW FPGA, a CLIP Node is a method to import custom FPGA IP (i.e., code) into a LabVIEW FPGA application. CLIP stands for Component-Level Intellectual Property. We needed to use special Socketed CLIP Nodes (i.e., VHDL that can access FPGA pins) for this project because we could expose additional features of the Xilinx Virtex-5 not exposed in LabVIEW FPGA by accessing Xilinx primitives. Some specific features were:

- Faster FPGA clocking

- Additional clocking options

- Individual clock and skew control

- Custom PLL de-jitter nodes

Essentially, the FPGA design had a majority of FPGA code developed in LabVIEW FPGA and we used CLIP Nodes for interfacing the signals between the FlexRIO and the FAM.

FlexRIO Adapter Module

As mentioned earlier, we had to create a custom FAM because of the need to route high speed signals from customer-specific high density connectors while synchronizing signals across multiple data channels and FPGA modules to within one (300 MHz) clock cycle.

At these high-speeds, the FAM needed careful buffering and impedance matching both on the signals as well internal components on the FAM PCB. At the start of the design, we utilized Mentor Graphics HyperLynx High Speed DDR signaling Simulation software to minimize signal reflections prior to building actual hardware. This step saved countless hours in spinning physical hardware designs.

We designed the FAM to allow channel routing and access to additional clock and trigger pins on the Xilinx chip and PXIe backplane.

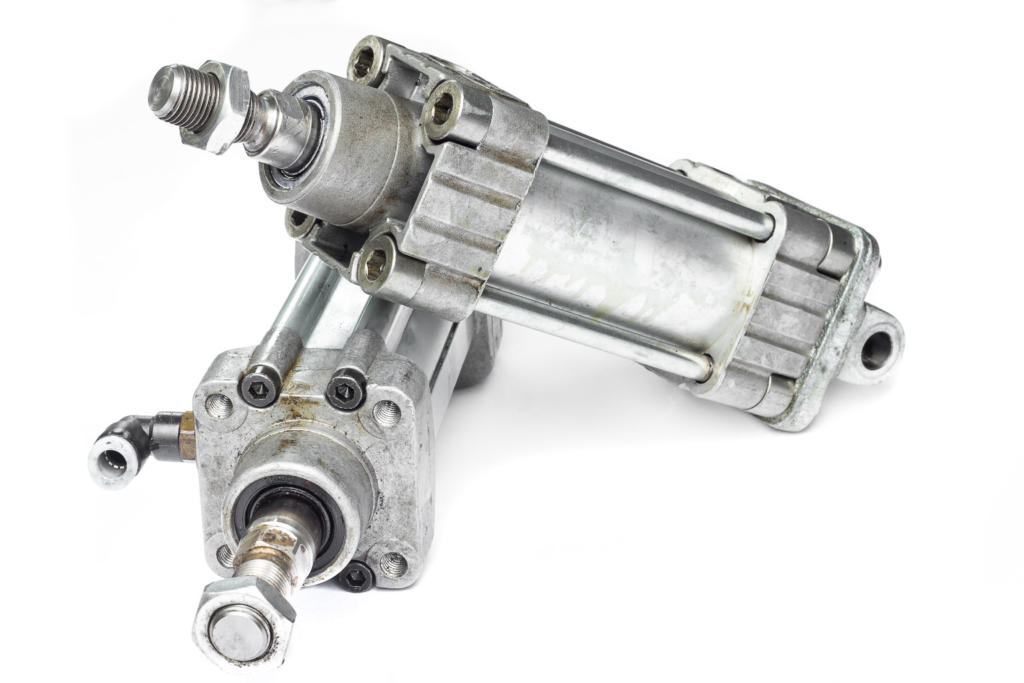

Endurance Testing using NI PXI

Endurance Testing using NI PXI

An automated system permits faster validation, unattended test, an increase in throughput, and can free up resources for other tasks during the weeks long endurance test.

Client – A manufacturer of aircraft components in the mil-aero industry

Challenge

New product development drove the need for a new aerospace endurance test system for product validation. The old systems were not designed to test the newly designed part (aircraft actuators), and the company didn’t have the time or resources to reconfigure existing systems to perform the testing required.

Solution

The new PXI-based endurance test system provides automated electromechanical testing, full data recording, report generation and a diagnostic panel for intelligent debug. Viewpoint selected the NI equipment, while the test consoles, and other components were selected and fabricated by the customer.

Benefits

- This automated aerospace test system permits faster validation, unattended test, an increase in throughput, and can free up resources for other tasks during the weeks long endurance test.

- Full data recording with a data viewer enables post analysis, which provides the ability to review and analyze raw signals captured during execution. Channel examples are actuator LVDT position, load, current, and encoder actuator position.

- Summary report capability allows the customer to document the amount of testing completed against the full endurance test schedules.

- A manual diagnostic operational panel provides the ability to verify particular DUT functionality or components without running an entire schedule.

- Systems can be paused and restarted to allow for “scheduled maintenance” of the DUT such as inspections, lubrication, etc.

System Overview

The PXI-based aerospace endurance test system enables data collection, deterministic PID Loop Control, emergency shutdown and a diagnostic panel for manual test and debug operation. The system runs endurance test schedules, that are defined as a recipe for test execution. These schedules, which are customer-defined and DUT-specific, are designed to simulate the actual conditions the DUT would see in real world application as closely as possible. LabVIEW-RT was used for the deterministic looping for Closed Loop Control of Actuator Position and Load Control. LVDT demodulation was performed on a PXI FPGA card programmed with LabVIEW FPGA.

| SOFTWARE FUNCTIONS |

|---|

| GUI |

| Summary Reports |

| Full Data Collection for Real-Time and Post Analysis |

| Deterministic PID Loop Control |

| E-Stop Management |

| Diagnostics Panel for Manual Test and Debug |

| Endurance Test Schedule Execution |

| Hydraulic Control Panel for Source & Load PSI Control |

| HARDWARE USED |

|---|

| PXI |

| Various PXI-based Data Acquisition Cards |

| PXI RT Controller |

| PXI FPGA Card |

| INTERFACES / PROTOCOLS |

|---|

| TCP/IP |

Endurance Tester for Mission-Critical Mechanical Component using NI cRIO

Endurance Tester for Mission-Critical Mechanical Aerospace Component using NI cRIO

Ability to run tests unattended and overnight reduces operator labor and compresses test schedules

Client – Major Aerospace Component Supplier / Manufacturer

Challenge

The client had an older VB & PLC-based aerospace test system in place already, but it was obsolete. A new endurance test system needed to be developed to validate prototyped components (in this case, aircraft & aerospace bearings). Many of the prototypes are one-off, so it was important that the test system not destroy the component.

Solution

A new endurance test system was developed to validate prototyped aerospace components. The test system can be configured for automatic shutdowns so as not to destroy the component under test in the event of unexpected performance of electro-mechanical subsystem components. The updated endurance tester supports product validation by allowing the product to run under various test conditions (e.g. speed, load, oil flow, temperature) and collecting data for analysis.

Viewpoint developed the software and selected the NI hardware (other hardware was selected by the client).

Benefits

Ability to run tests unattended and overnight eases operator labor and compresses test schedules

Data collection allows for offline engineering analysis

Automatic shutdowns reduce destruction of the prototype component under test

System Overview

The updated cRIO-based endurance tester incorporates configurable profiles, data logging, and automatic shutdown to allow for safer extended validation testing. LabVIEW FPGA and LabVIEW RT were used together to interface with the test hardware sensors and controls. LabVIEW as used create the HMI for the test system.

| SOFTWARE FUNCTIONS |

|---|

| Closed loop control of bearing test oil flow |

| Axial load control |

| Driver for Emerson VFD |

| E-Stop and safety management (shutdowns based on alarm limits) |

| Data collection – temperature, pressure, flow, vibration, frequency |

| Operator/Diagnostic GUI for control of system |

| HARDWARE USED |

|---|

| NI CompactRIO (cRIO) |

| NI C Series Current Input Module |

| NI C Series Voltage Input Module |

| NI C Series Temperature Input Module |

| NI C Series Current Output Module |

| NI C Series Analog Input Module |

| NI C Series Sound and Vibration Input Module |

| NI C Series Digital Module |

| Emerson VFD (Variable Frequency Drive) |

| INTERFACES / PROTOCOLS |

|---|

| TCP/IP |

| TCP Modbus |

Product Validation using LabVIEW RT & LabVIEW FPGA – Electromechanical Actuator Test Stand

Product Validation using LabVIEW RT & LabVIEW FPGA – An electromechanical test stand for an aerospace actuator

Automated testing reduces operator man hours and increases production throughput.

Client – A manufacturer of actuators in the mil-aero industry.

Challenge

New Product Introduction (in this case a new controller and new actuators) drove the need for a new aerospace electromechanical test stand.

Solution

New NI PXI-based electromechanical test equipment provided automated HIL testing, report generation, and SPC data generation. The sequencing of the test procedure, reporting, and verifiable results were managed with the StepWise test executive platform.

Benefits

- Automated testing reduces operator man hours and increases production throughput.

- Meets strict customer requirements regarding testing and data recording in a verifiable manner.

- Automated Test Report Generation.

- Collects data to support SPC (Statistical Process Control).

- Ability to interact with the internal state of the controller FPGA via the LVDS communication link.

System Overview

Viewpoint developed the software and selected NI data acquisition and control hardware for the test stand. There are several layers of software functionality.

| HOST LABVIEW SOFTWARE LAYER |

|---|

| Test sequencer |

| Test steps (e.g. Frequency Response, Step Response, Dynamic Stiffness, Fault Response, Power Consumption) |

| Test Report Generator |

| GUI |

| REAL-TIME (RT) LABVIEW SOFTWARE LAYER |

|---|

| Data acquisition |

| 1553 comms |

| Function generator |

| Error detection |

| ESTOP |

| LABVIEW FPGA SOFTWARE LAYER |

|---|

| Synch data from 3 sources (tester, UUT, external DAQ device) |

| Stream high-speed data to disk |

| Stream high-speed data to analog outputs for HIL test |

| Custom communication protocol used by UUT over LVDS lines |

| HARDWARE RECOMMENDED |

|---|

| NI PXIe |

| NI FlexRIO card with LVDS adapter module |

| Multiple NI R Series cards |

| High speed, high voltage, isolated analog input cards |

| INTERFACES / PROTOCOLS |

|---|

| MIL-STD 1553 bus |

| LVDS |

| Ethernet |

| Custom TCP/IP |

*- images are conceptual only, not actual

Product Validation & Production Test System – For complex Mission-critical sub-system

Product Validation & Production Test System – For complex Mission-critical sub-system

Upgrade reduces per unit test time by ~40% and improves reliability of software

Challenge

The customer needed to upgrade their existing test system. Their old test system was very manual:

- It did not provide ability for unattended operation

- The thermal control had to be set manually

- They wanted to do less manual review of the data

The client develops mission-critical products, so there’s a desire to reduce manual operations because they have to explain any anomalies, and manual operations are typically more error-prone. They needed repeatable results that they could trust.

Solution

Viewpoint developed a new test system that utilized new hardware and software, augmented by existing low level hardware and firmware. The test system was developed to perform both functional test for production and environmental testing, and was designed to handle up to 4 DUTs at once. The test system utilizes the StepWise test executive software with custom test steps, which allowed the client to create their own highly configurable test sequences. The system was developed in two phases, with the second phase adding support for a FPGA expansion backplane (NI CompactRIO chassis) in order to provide future capability for bringing some of the microcontroller sequence activity into the NI space. In addition, the previous version had a mix of serial, TTL, and USB instrumentation, which was not as robust as Ethernet based instrumentation. Phase II involved upgrading to all Ethernet based instrumentation, and did away with the original test system’s many manual toggle switches that could be used instead of the programmable mode through the SW.

Benefits

- ~40% test time reduction per unit

- ~25% reduction in anomalies that needed to be justified

- ~500 manhours saved in test execution

System Overview

| Software Functions |

|---|

| Test sequencing |

| Test report generation |

| Data recording/logging |

| Error handling |

| Test GUI |

| Oscilloscope interface |

| Thermal chamber interface |

| Power supply interface |

| External custom hardware interface |

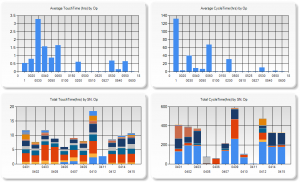

Hidden Factory Assessments Lead to Waste and Cost Reductions

Sharing Business and Test Data Enables Efficiency Improvements

Reduce Production Costs by Coordinating Business and Test Data

Client: A major manufacturer of aerospace components

Problem Scope

Many companies operate in a high-mix, low-volume manufacturing environment. In these situations, production of such parts is often complex, with long assembly and test procedures describing the process to make and verify the part. Discussions of automating any part of these processes are often dismissed because an automated test system is thought to be expensive, especially an aerospace test system which requires significant documentation and acceptance testing efforts. Plus, it’s often erroneously thought that each part needs a unique test system.

Challenge

Our client wanted to improve their capability to manage the assembly procedures and get clarity on the status of any parts, whether partially or fully assembled. The existing situation had data manually-entered into a database form or even handwritten data that needed to be transcribed into a database. Often the database was local to the assembly cell. The chance for error was significant and the lag between data collection and updating the database was often days. When questions arose about the status of a particular unit, many hours could be spent in locating and evaluating the associated forms and paperwork.

The steps needed to achieve these goals were clear: automate the collection data on each part while being assembled so that those results would appear in a business-level database which would give a plant-wide view of the status of all the parts in progress.

Thus, this project needed to allow read/write access to sections of the Manufacturing Enterprise System (MES) database so that information about a part being assembled could be obtained automatically and results could be submitted to that MES database automatically.

Solution

We designed the PXI-based system based on the StepWise test executive platform to automate the assembly and testing. This platform enables two significant changes. These changes were made at each assembly cell by having the operator use a test PC and perhaps some measurement equipment as appropriate for the part(s) being assembled at that cell.

First, we replaced all the printed assembly procedures with electronic records so that any operator could review the latest version of the work instructions on a computer screen. This approach helped with version control, especially important since the client had various model revisions that came through the factor for rework, each with slightly different versions of assembly instructions.

Second, we displayed those electronically documented work procedures as steps in a test executive, allowing the results of each step in the assembly procedure to be captured electronically. When an assembly step was purely manual with no measurements, the fact that step was completed would be recorded, along with information such as the name of the operator performing the step, the duration that the step took, and so on. When a step required a measurement to be made, such as a functionality verification or a calibration result, the measurement would be collected. If the equipment making that measurement could be automated, we would collect that data automatically, and not require the operator to type the result into a computer form.

The outcome of this effort has enabled the client to get a snapshot of the status of parts in assembly, i.e., Works in Progress (WIP), quickly and accurately.

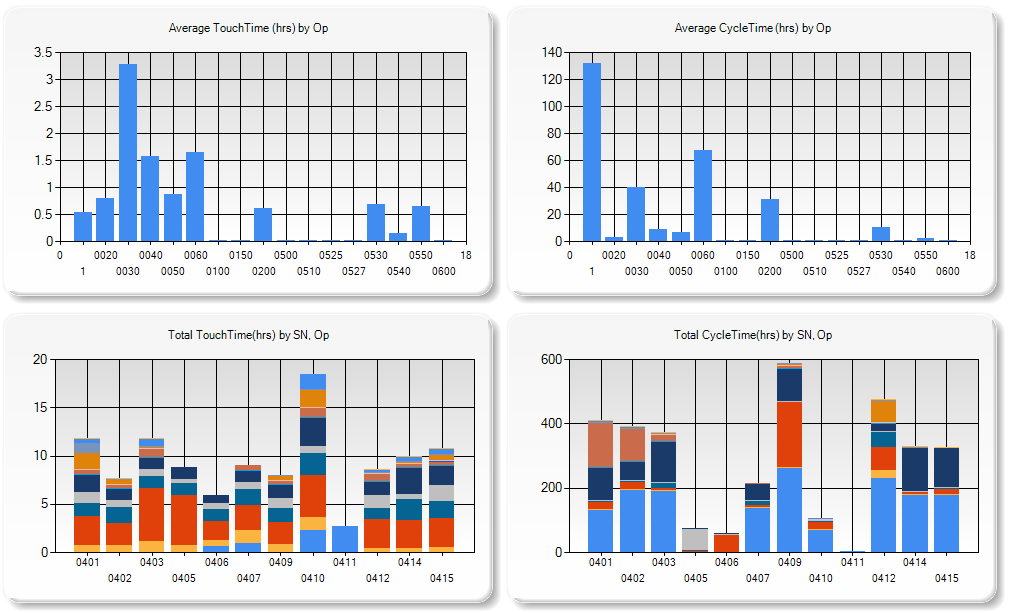

After these changes were made, many additional capabilities are now available with the advent of purpose-built queries into the appropriate MES database tables. The table below shows the overall efficiency gains achieved.

The key is the combination of the electronic test results obtained at the test equipment with information on work orders and manufacturing flow held in the various tables in the business MES database. This improvement happens even with manual or semi-automated test systems, and does not require a completely automated assembly and test system. Thus, the cost of the test system is much less than usually expected and, hence, the benefits are more easily cost-justified.

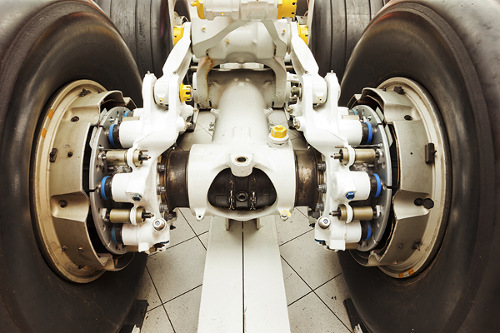

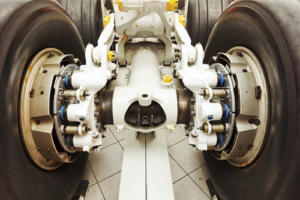

Decreasing Test Time for Aircraft Landing Gear

Decreasing Test Time for Aircraft Landing Gear

Endurance Testing for Aircraft Nose Landing Gear Steering

Client: A major manufacturer of aircraft landing systems

Challenge

A major manufacturer of aircraft landing equipment needed to develop a means of endurance and fatigue testing new designs for aircraft steering. The actuators involved in steering the nose landing gear (NLG) required precise and reliable control through thousands of steering cycles.

Control loops needed to be closed at faster than 1 ms.

Prior systems were handled manually without real-time control and monitoring.

Solution

Our customer designed and built a test rig to provide the hydraulics and environmental conditions for the endurance testing on the NLG. Viewpoint Systems supplied the electronic data acquisition and control hardware coupled with real-time software to provide the required fast control loops. The configuration and execution of the 1000s of steering cycles were managed by the same data acquisition and control system through a set of configuration screens that allowed specification of turn rates, min/max angles, drive and resistive torque settings, and so on. The flexibility offered with this HIL test capability mimicked the variety of conditions that the NLG would encounter in actual use.

- The various PID control loop configurations were also configurable along with gain scheduling required under different operating conditions.

- The environmental conditions were supported by controlling a temperature chamber through ramp and soak settings occurring during the steering tests.

- Measurements on the steering performance were collected from commanded setpoints, sensor readings, and controller outputs during the entire test run.

- Alarm and fault conditions, such as force exceedance, were monitored continuously during operation so that the system could safely run unattended.

Since the deployed solution was an aerospace test system, the entire system underwent an extremely rigorous acceptance testing procedure to verify proper and safe operation.

| SOFTWARE FUNCTIONS |

|---|

| Arbitrary Load and Position Profiles |

| Flight Position Control |

| Load Position/Force Control |

| Endurance/Flight Schedule Execution |

| Deterministic RT for DAQ and PID Control |

| HARDWARE |

|---|

| PXI/SCXI Hybrid RT Chassis |

| Discrete Pump Skid Interface |

| Custom Control Panel/Console |

| INTERFACES |

|---|

| Ethernet TCP/IP |

| SCXI |

Results

Prior to deployment of our system, setup of a test was much more manual and operators needed to be around to monitor operation.

With our new system, complete endurance testing could be specified and executed with minimal supervision. Furthermore, the tight integration of real-time control, HIL testing, and coordinated data collection made report creation much simpler than before.

The rigorous acceptance test gave trustworthiness to the data and allowed the design engineers to validate performance more quickly than the prior semi-automatic and manual methods of operation.

Setup of tests has been improved from prior operations. The endurance testing itself operated over a huge number of cycles lasting weeks to months between scheduled lubrication and maintenance.

The deployed system measures performance during the entire testing, even between the scheduled downtime.

If you need a custom test system for your mission-critical aero-def component, reach out here.

Want to learn how to make your assembly and test process a competitive advantage? Check out this webinar »

Poll – Test engineering leaders: What would help you most? Vote and see how your peers voted!

Designs need to be extensively validated, and manufactured products require comprehensive testing. In contrast to aero-def products from the early 2000s, an increasing number of products now use embedded controllers. Such products require interfacing to electronic components in order to test the combined mechanical and electrical performance of the entire system. Products often need the test system to simulate the surrounding subsystems and/or environment in order to assess performance in as realistic a situation as possible. These simulations are usually handled by either Hardware-In-the-Loop (HIL) or Software-In-the-Loop (SIL) subsystems. Depending on the levels of allowed latency and jitter levels, the HIL simulation may run on either or both of an FPGA or an RTOS that supports hardware I/O. The SIL simulation will almost always need an RTOS.

We’ve helped teams at some of the world’s most innovative companies