Automated production test of EO/IR imaging subsystem

Assessing quality of mission-critical electronics for imaging

Increased throughput by automated signal skew adjustment and pixel verification

Client – Worldwide supplier of products for aerospace and defense

Challenge

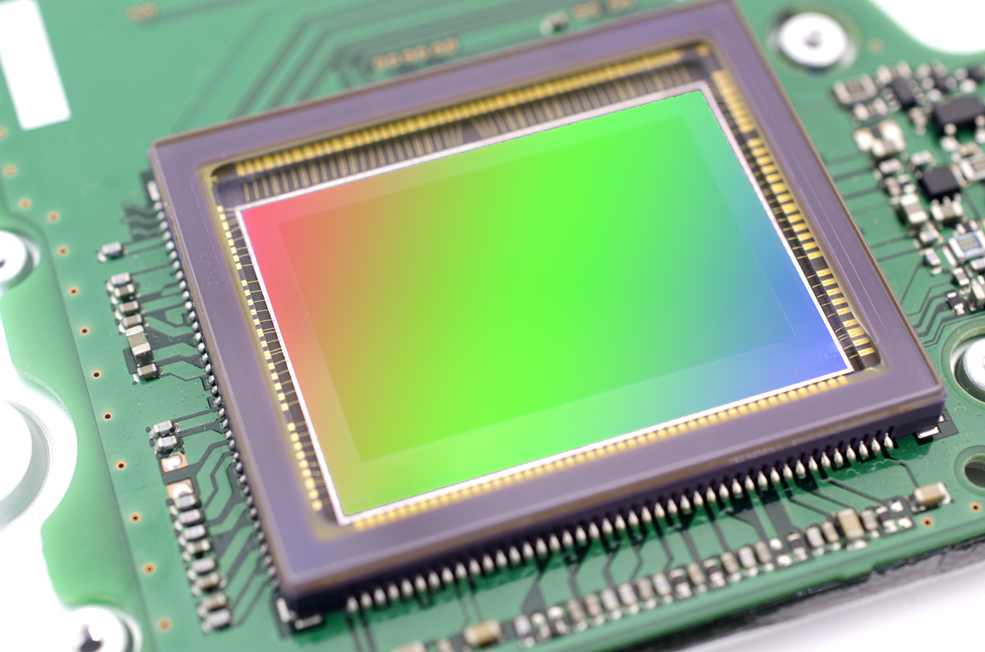

Our client wanted a test system that would significantly increase production rates for a very specialized focal plane array (FPA) and associated readout integrated circuit (ROIC) electronics.

In broad strokes, the system needed to support the following:

- Increase production test throughput as much as reasonably possible within budget and schedule constraints.

- Provide some low-code or no-code way to create new test protocols.

- Protect the DUT using hardware and software interlocks.

- Verify the correctness of test image(s) and all its pixels.

Solution

The FPA and ROIC testing for this client used many of the same techniques we have implemented for FPA/ROIC testers at some of our other clients. Thus, the solution was built around our AEDIS platform and some custom connectivity hardware which paired the DUT to the AEDIS hardware.

Specifically, the test needed to:

- Send digital signals from the AEDIS hardware to initiate and coordinate the test steps.

- De-skew bitstreams from the DUT.

- Organize and rearrange the bitstreams into image pixels.

- Provide custom “personality” modules to connect the DUT and AEDIS hardware.

- Protect the DUT from connection and power faults.

Benefits

All the bulleted items above are common requests from our clients and are supplied with the AEDIS platform or easily accommodated by design of the platform. Consequently, AEDIS often meets 80% or even 90% of typical client needs.

Thus, the client was able to cost-justify an AEDIS-based solution for two main reasons:

- overall system costs for an AEDIS-based solution were significantly less than a completely custom system and

- the increased production rates provided plenty of schedule buyback.

Furthermore, the script-based, low-code capabilities offered by AEDIS enabled:

- Support of different test images.

- Control of image transfer initiation, handling responses from the DUT, and flow.

- Version control (by the client) of script-based test configurations.

- Defined parsing of bitstreams to create the image pixels to simplify downstream image collection.

System Overview

The test system was built around AEDIS, which is a combination of five major components:

- NI FlexRIO PXI modules and chassis.

- Signal conditioning hardware.

- A REST API interface for the client’s test sequencer and LabVIEW FPGA for the hardware interfacing.

- An out-of-the-box browser-based app to interact with the AEDIS system.

- A source measure unit to supply and test the DUT’s power needs.

With this design, AEDIS acts as an instrument to incorporate into the client’s overall test system.

The NI FlexRIO modules use Xilinx FPGAs for digital I/O at the rates and channel counts required to fully test the FPA on the DUT. Some digital lines were used for commands to the FPA while most were used to receive output from the FPA.

The AEDIS interfacing hardware acts as an ITA while converting the FPA/ROIC signals to types expected by the FlexRIO. A custom “personality” module provides the physical connectivity from the client’s hardware cabling to the ITA. The AEDIS software handles the test configuration setup, data acquisition, and data storage via high-speed RAID drives.

During development of the test system, AEDIS hardware and software were also used to emulate the actual FPA and electronics to verify, before deployment, that the test system was working as required. This same setup can also be used for periodic verification as might be needed for an annual equipment performance audit.

Finally, configuration files were built from user-created scripts to give the client flexibility for adding new test capabilities for the DUT.

Some of the significant hardware and software challenges mitigated by this combination of PXI FlexRIO and AEDIS are:

- Interface to tester: The AEDIS system is treated as an instrument managed by an overall test system. The client developed some custom C# code to interface to the AEDIS REST API interface to automate their test procedures.

- DUT interfacing: Standard (keyed) cabling ran between the DUT and the custom AEDIS “personality” card to match cabling to the DUT. The output of this personality module went to the AEDIS LVDS modules.

- Channel skew: The high-frequency digital LVDS signals from the DUT can develop noticeable timing skews between channels upon arrival at the FlexRIO inputs due to signal path length differences. The test system had to detect and accommodate for these skews before combining the bits streams into bytes, then pixels, then an image.

- High data rates: Not only were the digital data output at high frequency but many channels were needed to accommodate the full frame rate of the DUT. The FPGA and the PXI backplane needed enough processing and transport bandwidth to accommodate the throughput.

- Interlocks: Keyed cabling and “signal present” software checks assured proper connections between the DUT and the AEDIS hardware before testing would begin. These safety checks were justified due to the high cost of each DUT.

- User-defined scripts: Scripts created and edited by the user provided flexibility to address future test types and system obsolescence. For example, the scripts defined details such as a) the DUT-specific commands (some of which could not be shared with us for secrecy reasons), b) when the image is being captured (or ignored), and c) if the image is stored to disk or RAM.

| SOFTWARE FUNCTIONS |

|---|

| Browser-based app for manual operation and recipe creation and editing |

| REST API interface for support of automated operation |

| Configuration of the test via scripts |

| Pre-test interlock checks |

| Data collection, bit stream processing, and mapping digital bitstream to pixels |

| HARDWARE USED |

|---|

| Standard AEDIS components for signal buffering, conditioning, and signal acquisition |

| Custom personality hardware for connectivity and physical connection interlocks |

| Signal test points in AEDIS breakout ITA modules enabled use of a logic analyzer for troubleshooting and further verification |