Test system development – sometimes custom electronics are better than COTS

When, why, and how we think about it

COTS products are great! There’s a reason they exist.

They:

And yet, in some situations, custom electronics can be a better fit for your test system.

The fundamental drivers for why custom make sense situationally are:

- Extra functionality – Custom often makes sense when the COTS components bring along more features than necessary. All those extra features cost more money, add points of failure, and can increase the difficulty in integration and maintenance of the test system.

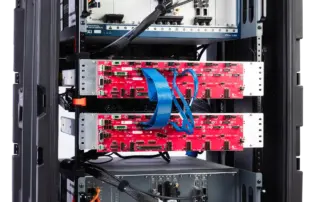

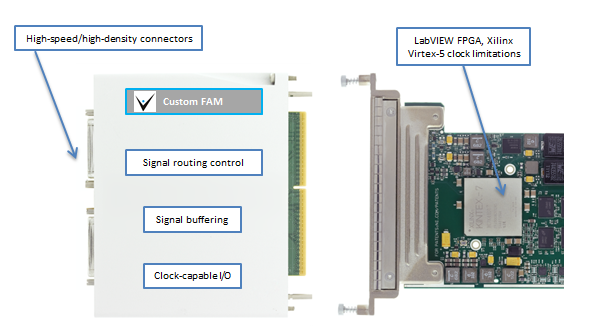

- Performance limitations – Because COTS products are trying to meet the needs of so many scenarios, they may be limited for specific needs. add a microcontroller and an FPGA to some front-end custom electronics, and tasks difficult to perform in COTS can be made much easier. For example, using an FPGA to return timestamps of digital state changes across 100s of digital channels reduces data bandwidth that would otherwise be streamed across a PC bus.

- SWaP (Size, Weight, and Power) requirements – . A small, light-weight, and/or low-power test system may be preferred due to environmental constraints. For example, measurements made in a small chamber make I/O cabling difficult or the DUT moves during testing and a small, low-power wireless DAQ device can be mounted right on the DUT.

We’ve helped our clients identify custom test solutions that, because they are laser-focused on a particular testing need, can be cheaper, more easily deployed, or have higher performance than a COTS solution.

Custom is situationally preferrable to COTS for test because you can potentially:

- Save $ during development

- Save time during development

- Save $ in maintenance

- Improve reliability

- Improve performance

- Improve SWaP (Size, Weight, and Power)

How we identify opportunities for custom electronics

After we’ve engaged with our client and obtained a good understanding of the test needs, we start choosing the measurement and control hardware needed to execute the test plan. Those details include:

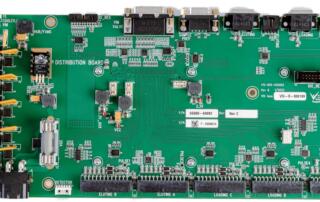

From this list, we start by looking for any sensors, such as thermocouples for temperature or accelerometers for vibration, followed by the equipment to digitize these signals. If control is needed, we do the same for output actuators.

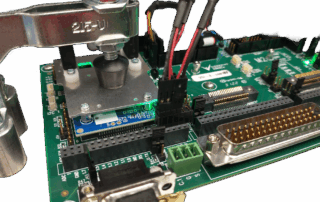

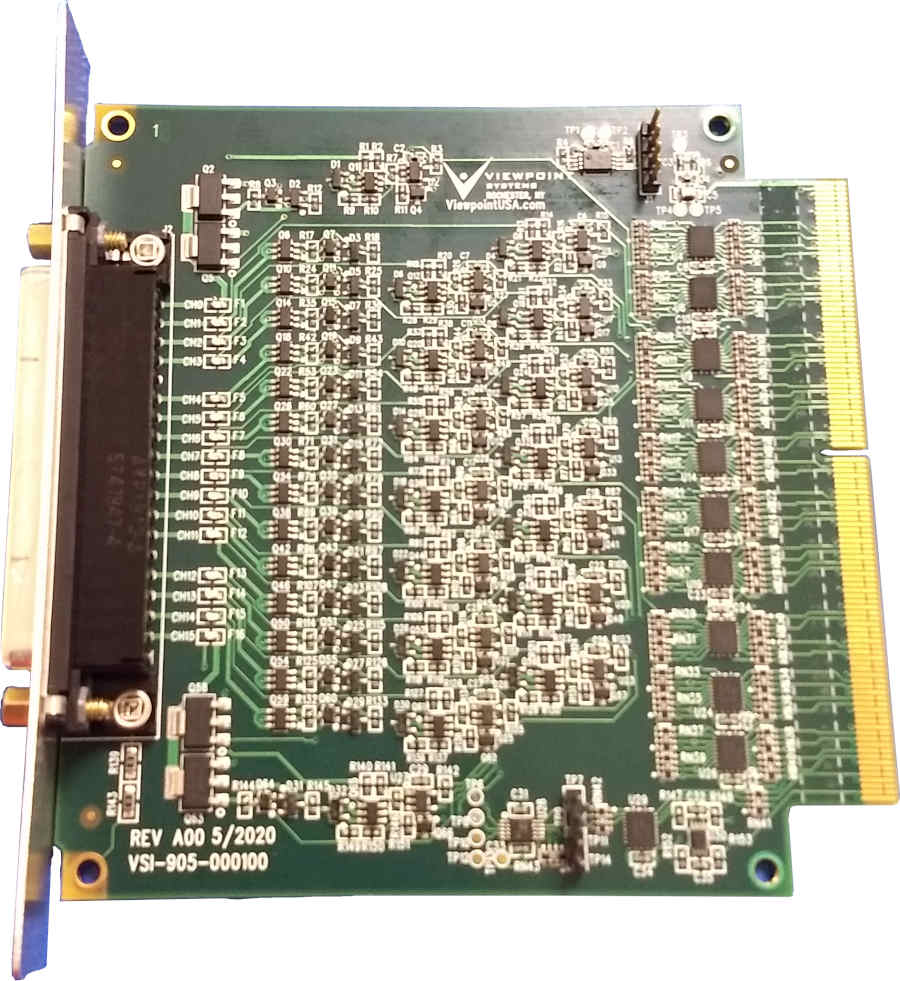

For the complex measurements, we will decide if basic digitization of sensor output can be coupled with either sophisticated circuitry or compute capability via FPGA or microprocessor. This type of combination may replace several COTS components with lower cost, physical space, and power needs. For example, we can produce a “smart sensor” by measuring two analog inputs, correcting non-linearities, and then performing some calculations to produce a measurement of torque differential.

Then we look at how to connect it all together and how to power it.

During this process, we look to COTS hardware first. If we spot possible opportunities to save cost, reduce development time, increase reliability, or improve performance by going with a custom electronics approach, we’ll proceed to dig into the details. Of course, spotting these opportunities initially relies on some gut feel and experience where we sense that custom electronics might be a better solution. Many times, it’s not. But often enough the benefits are outstanding.

Below are some details about areas where we see these benefits.

Save $ during development

Examples of how:

- A custom PCB can be less expensive than complex harness configurations. Point to point connections still need to be made manually, but making a PCB is a lot cheaper than building an actual harness.

- A microcontroller or an NI sbRIO can reduce system cost compared to an expensive PXI card of which only a few channels or a small subset of features is needed.

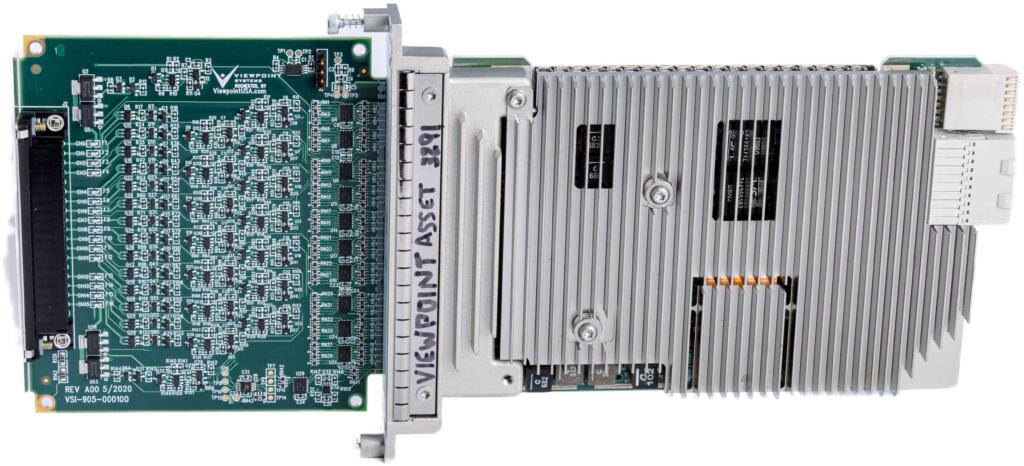

- A custom front-end to a COTS NI cSeries card can be less expensive than a set of COTS signal conditioning modules and offer better field connectivity.

Save time during development

Examples of how:

- Modular pre-designed subassemblies can be combined for quick turnaround. For example, common blocks like power regulation, A/D, D/A, DIO, and so on can be plucked from a schematic library and incorporated quickly into a new custom design.

Save $ in maintenance

Examples of how:

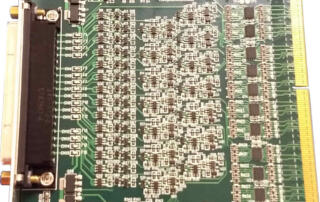

- Custom PCBs are more reliable than custom cable harnesses and can be less expensive to build.

- Circuitry can be added to allow software access to hardware parameters and calibrations to simplify validation and calibration.

Improve reliability

Examples of how:

- Custom PCBs can be more reliable than custom cable harnesses.

- Custom PCBs or microcontroller-based subsystem can reduce system part count and hence reduce the number of failure modes.

- PCBs can control impedances of signals, giving better signal integrity.

Improve performance

Examples of how:

- A COTS solution doesn’t exist, e.g., a fast 28 VDC digital input module

- A custom front-end can improve precision by boosting signal-to-noise

- Remote, high-performance, critical circuitry can deliver the desired signal types without relying on expensive long-distance sensor or actuator cabling.

Want to see some case studies where custom electronics were leveraged for test systems?

Next steps

Want to see if custom electronics makes sense for your automated testing needs?

Reach out here to see how we can help:

COTS products are great. In fact, during test system design and hardware selection, we look to COTS component first to take advantage of and leverage them whenever it makes sense. If you need help selecting NI-based test hardware, check out our NI hardware selection services and reach out if you’d like help. If we see a situation where a custom solution will be better suited and as or less expensive than COTS, we’ll want to discuss with you about pros and cons of using custom electronics for test.